上一篇最后,我们说要解决PI的问题其实就是解决I(f)和Z(f)的问题,而Z(f)更为重要。因为一个芯片其工作时候的电流行为通常...

上一篇最后,我们说要解决PI的问题其实就是解决I(f)和Z(f)的问题,而Z(f)更为重要。因为一个芯片其工作时候的电流行为通常是不易改变的。比如你使用的是一颗无线芯片,其工作的时候,在基带载波的频点总是有一个比较高的电流能量,这点不易改变。而如果想V(f)小的话,那就只能优化Z(f)。这里的Z(f)是电源网络的阻抗,也叫PDN。这个阻抗一般很小,是在mohm到几ohm量级,它代表从VRM到Die的全链路。另外需要注意的一点是PI主要讨论的是AC值,PDN的好坏直接影响到电源的噪声V(f)。

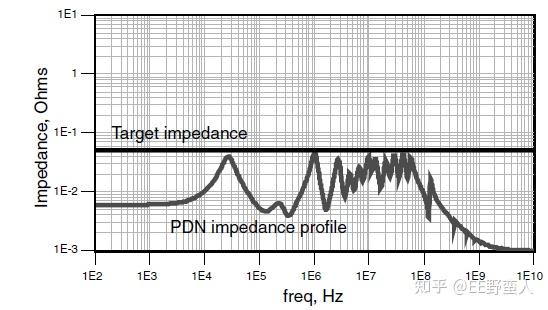

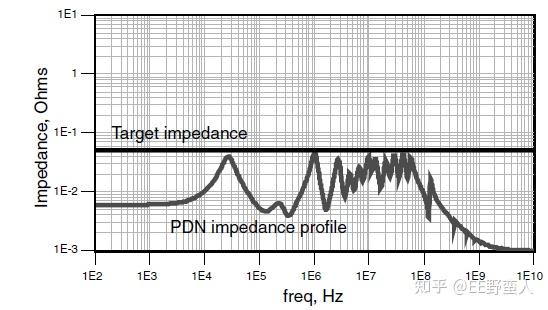

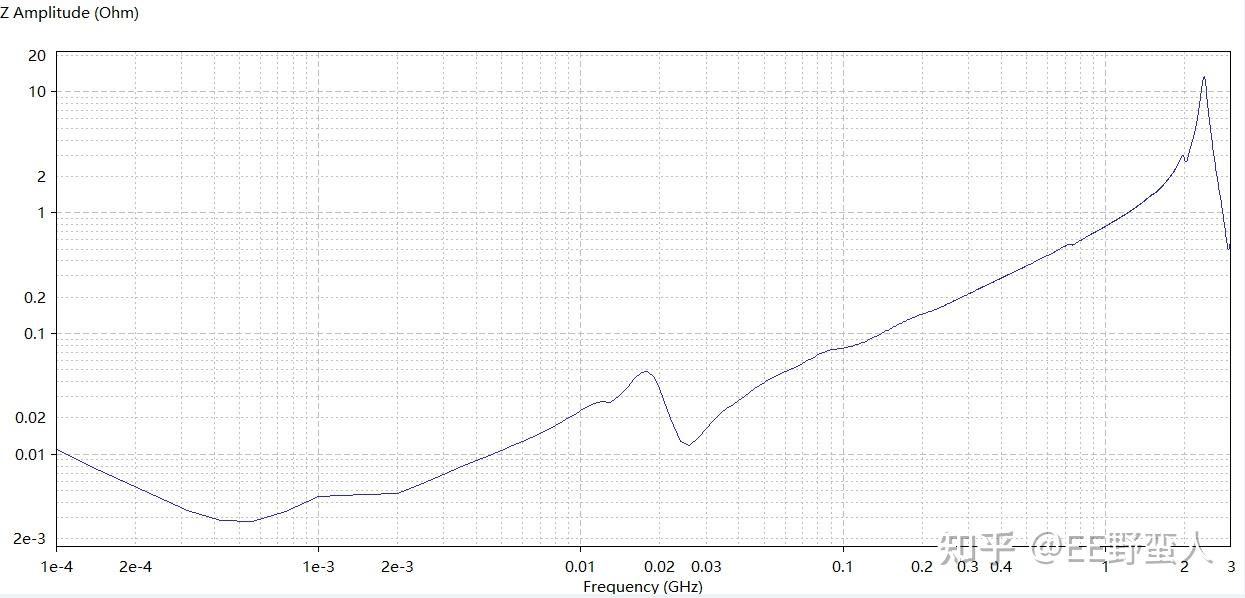

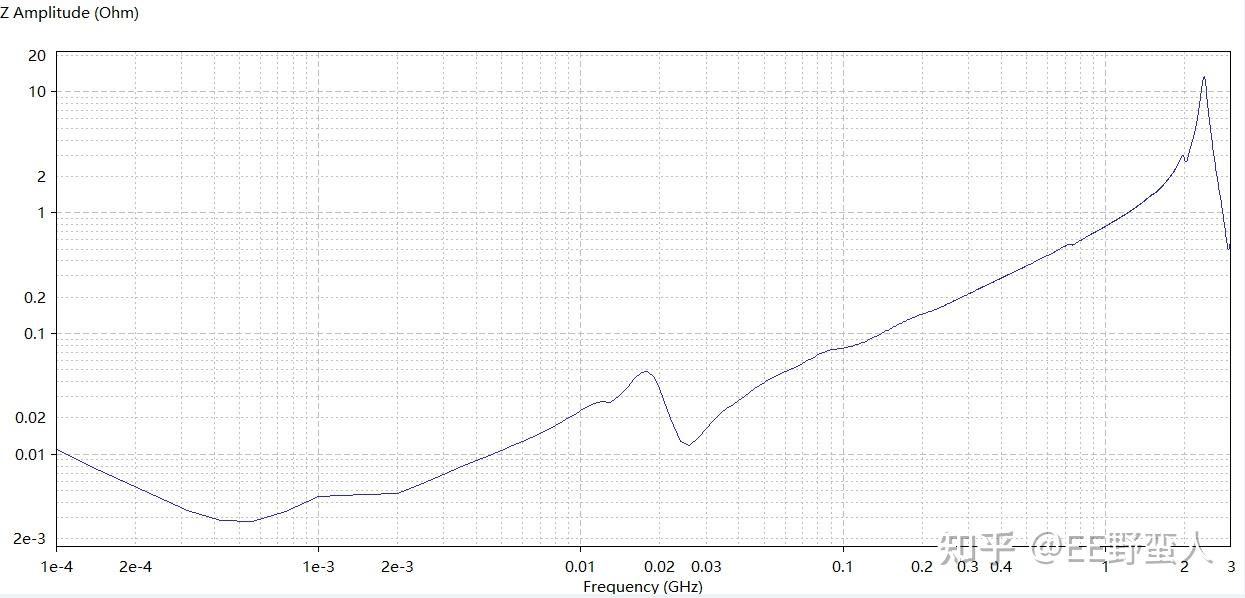

很多书上面都会介绍一个Ztarget的概念,就是你要让电源链路的PDN的这根阻抗曲线的最高点控制在多少的Ztarget以下才能满足Vripple的Spec要求。就如下图这个PDN曲线例子一样。

这里假设电流的最大瞬态变化量Itransient,在PDN的最大值的时候,相乘得到最大的电压波动<Spec的要求(Vdd x Ripple%)。一般芯片要求的电源ripple都在3%~5%左右,这个PDN的最大值就是Ztarget。但是对所有频点的PDN都按照Ztarget来要求是比较严苛的。其实你能得到芯片原厂提供的芯片电流行为数据或者频谱,那就并不需要对PDN设置一个Ztarget的约束,而直接以最终时域噪声大小的仿真结果(Z(f)*I(f)的结果)来判定PDN是否OK即可。当然前提是你得有I(f)的数据,而这个一般非芯片厂商是不容易得到的。

接下来我们围绕几个问题来研究下这个PDN,我觉得这几个问题真理解了,也就懂PDN了。

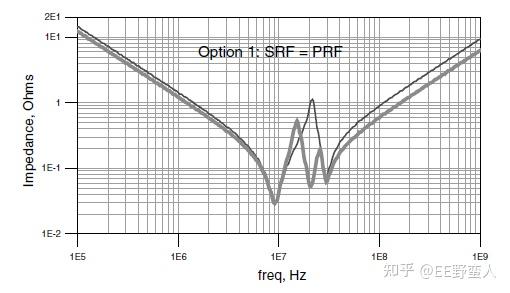

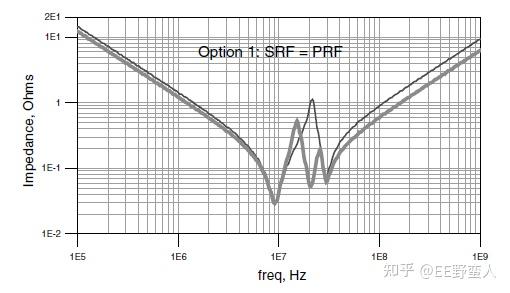

- 如何降低PDN的反谐振峰?

降低Ztarget其实就是压低反谐振峰。在上一篇,我们已经知道这个PRF是怎么产生的。但是产生了如何去压低它呢?比如下图,深色PDN有两个电容组成,它有一个反谐振峰,通过找一个自身SRF的频点接近这个PRF频点的电容加入到这个PDN中就可以起到把反谐振峰压下来的效果,如下图浅色曲线PDN。工程上一般是按照这个原则作为挑选电容优化PDN的首要原则。两个电容并联的情况是如此,很多个电容和电源平面的PDN也是如此。有反谐振峰的地方,如果超过Ztarget,那就要把它压下去。

2. 也许有的人会问那上面图中曲线,左右两边,都比谐振峰还要高怎么处理呢?我们一个一个说

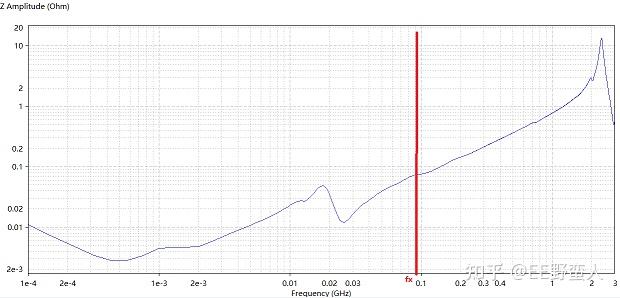

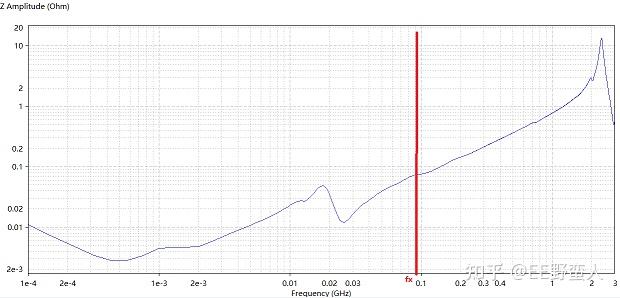

第一,先谈左边的部分。其实真正的PDN曲线,由于VRM通常具有低输出阻抗,加入到PDN曲线之后,会使得整个PDN曲线在低频KHz频段都是平坦的,因为这个时候VRM的低输出阻抗在起主导作用,如下图,这是从一块PCB上提取出来的一个电源网络的PDN,使用的Sigrity。

可以看到曲线在低频到几十兆Hz的频段PDN都比较平坦,在0.1ohm以下,没有太高的反谐振峰。这个时候就不是两个电容并联的情况那么简单的曲线了。

第二,再谈右边的部分,右边单调增加的高阻抗怎么办? 可以从上图中看到,PCB的PDN中在高频段也会阻抗增加,在2G的位置就有一个很高的反谐振峰了。也许有人就会说,是不是按照上面说的方式,去找SRF=2G左右的电容去加进去吧。其实不然,上面说的方式,加电容,首先需要看这个PRF的频点所在的位置,根据这个PRF的频段判断一下它处在哪个位置,是PCB级,Package级,还是Die级?不同位置的电容能处理的PRF不同,比如这里2GHz位置一般应该是封装级的电容才能处理的,你在PCB级上加一个SRF=2G的电容,也许这个电容根本就是多余的,起不到任何作用,这就要谈下一个重要的问题。

3. PCB板级的电容只能处理到几十兆Hz以下,再高频的噪声只能由芯片内部电容来处理。处理噪声频段的高低跟电容的位置还有关系。这该如何理解?

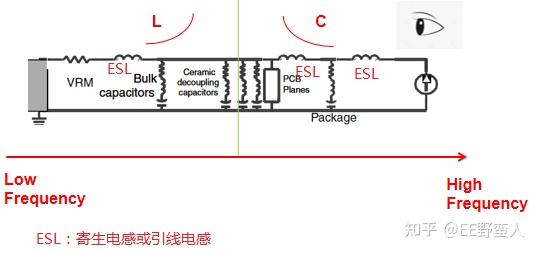

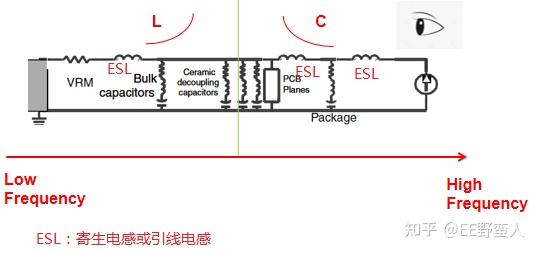

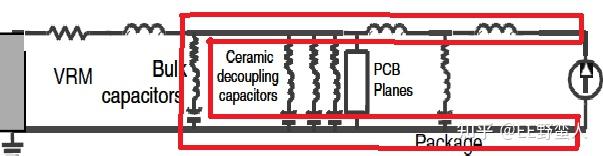

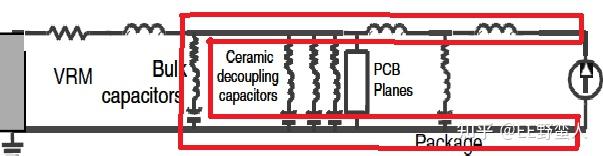

我们知道整个PDN是由PCB电容,Package电容,包括平面电容和Die上面的电容并联在一起,形成了PDN。但是也不要忘记了,将这些电容连接在一起的电源铜皮,下面图中水平方向上的那些小电感的存在(并没有画全,实际每个电容之间都有这种ESL)。毕竟只要有连线就会有电感的存在。

当我们用芯片的视角去审视PDN的时候,会发现只有离Die最近的电容在芯片看来才是一个电容,或者说更单纯,当芯片往离它远的地方看的时候,比如看那个Bulk Capacitors的时候,芯片所看到的是很多很多个水平的小电感串联之后,再到这个Bulk Capacitors。很容易想象,这个Bulk Capacitors在连接到Die上之后,Die所看到的,并不是单一的这个电容,而是到达这个电容的引线电感与电容的串联得到的总阻抗。如下图红色框圈起来的总阻抗。

所以电容位置离得Die越远,这个引线的电感也就会越大。其他所有连在PDN上的电容都是如此。好了,知道了从芯片视角看到的实际的电容与这个电容本身不是同一回事,原因就在这个引线电感上面。那么为什么离Die越近的电容负责越高频段的PDN阻抗?也就比较容易理解了。离Die越远的电容,引线电感越大,离Die越近的电容,引线电感越小,当然在Die眼皮底下的电容也就Die上的电容当然是引线电感最小的地方,所以这里的电容才能真正发挥自身的特性,不受引线电感的影响。所以总结来说由于引线电感或者ESL的存在,使得离Die远的电容,其阻抗将不可避免的被ESL所主导,在超过一定频率之后,其自身的电容是多少已经不重要了,重要的只是ESL。当然电容自身也有ESL,但是与这里说的电源铜皮导致的引线电感并不是指同一个东西,要区分一下。有时候因为都是寄生电感,也会把引线电感叫做ESL。

上图中的绿色线,它就像一根分割线,切在PDN的网络上,把PDN切成左半面和右半面,同时它与下面的红色频率轴相交,代表某一个频点。我们可以想象一下这根绿色线向右,频率高的位置移动的时候,从Die的视角看PDN,总是它左半面的部分先呈现感性(L),而右半面的部分呈现容性,也正是因为右半面的存在,才使得左半面的L和右半面代表的C形成了反谐振峰,遏制了左半部分L阻抗随频率单调增加的趋势。在频率达到很高的频率的时候,或者说绿色线移动到最右侧的时候,通常是上GHz,从Die的视角看过去,PDN上的其他所有都将是一个电感,只有Die上的电容才是最后的救世主,才会呈现真正的容性。这也是为什么电容能处理的频率范围还要看电容在整个PDN上的位置的原因。

4. 那么接着下一个问题,上面那张PCB的PDN的曲线图,虽然2GHz的时候,阻抗很高,当时说在PCB板上加电容通常是多余的。上面也解释了,不同位置处理不同频段的原因。毕竟这个只是PCB级的PDN的仿真结果,它只是相当于那根绿色线移动到某一个频点之后,左半面的PDN,而缺失了右半面,也就是缺失了Package级别的PDN和Die的PDN的信息没有级联上去,两者相加才是完整的全链路PDN。如果有了Package和Die上的PDN也许那个2G左右的反谐振峰根本就不存在了。

那么先把问题简化一下,只考虑PCB的话,怎么判断PCB的PDN考虑到多大频率fx之前就可以了呢?如下图,红色线fx频点后的部分对于PCB板级电容就已经无法处理了,那就交给Package和Die的电容去处理吧。我们下一篇在接着聊。

关注微信公众号:电子工程师那些事儿

慢慢带你建立起软硬件开发的系统观

如果认为本文对您有所帮助请赞助本站